Heterogeneous SiP devices integrate HBM2 DRAM with FPGAs

Altera has revealed the industry’s first heterogeneous SiP devices that integrate stacked HBM2 (High-Bandwidth Memory) from SK Hynix with high-performance Stratix 10 FPGAs and SoCs. Stratix 10 DRAM SiP represents a new class of devices that is specifically architected to meet the most demanding memory bandwidth requirements in high-performance systems.

Stratix 10 DRAM SiP will offer over 10 times higher memory bandwidth relative to discrete DRAM solutions that are available today. This unprecedented level of bandwidth is required in datacentre, broadcast, wireline networking and high-performance computing systems, which are processing an ever-increasing amount of data.

Altera is the first company to integrate this breakthrough 3D stacked memory technology alongside an FPGA. Stratix 10 DRAM SiP enables users to customise their workloads and achieve the highest memory bandwidth in a power-efficient manner. Altera is actively working with over a dozen customers to integrate these DRAM SiP products into their next-gen high-end systems.

Altera is the first company to integrate this breakthrough 3D stacked memory technology alongside an FPGA. Stratix 10 DRAM SiP enables users to customise their workloads and achieve the highest memory bandwidth in a power-efficient manner. Altera is actively working with over a dozen customers to integrate these DRAM SiP products into their next-gen high-end systems.

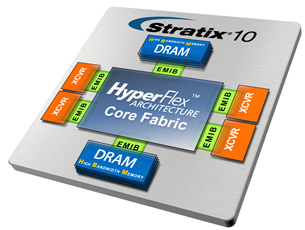

Heterogeneous SiP products from Altera are enabled by using Intel’s Embedded Multi-Die Interconnect Bridge (EMIB) technology. EMIB technology uses a small high-performance, high-density silicon bridge to connect multiple die together in a single package. EMIB technology features very short traces between die, allowing Altera to cost-effectively build heterogeneous SiP devices that provide higher performance and higher throughput at lower power compared to interposer-based solutions.

Danny Biran, Senior Vice Presiden, Corporate Strategy and Marketing, Altera, commented: “Supporting higher memory bandwidth requirements is one of the biggest challenges many of our customers face as they implement more computationally intensive tasks in their systems, such as machine learning, big data analytics, image recognition, workload acceleration and 8K video processing. Altera is in a unique position to serve these system requirements by combining the industry’s highest performance FPGA with HBM2 in a single package. No other programmable solution can match Stratix 10 DRAM SiP in terms of performance, power efficiency and memory bandwidth.”

Altera’s heterogeneous SiP strategy is to integrate into a single package a monolithic FPGA with advanced components, such as memory, processors, analogue, optical and various hardened protocols. Altera’s highly integrated SiP products will address the most demanding performance and memory bandwidth requirements for high-end applications in the communications, high-performance computing, broadcast and military segments.

SK Hynix’s HBM2 provides very high bandwidth while using less power in a substantially smaller form factor compared to competing memory solutions. HBM2 vertically stacks DRAM die and interconnects them using TSVs and microbumps. Integrating the HBM2 in a heterogeneous SiP implementation enables Altera to package the DRAM memory as close to the FPGA die as possible, which shortens wire length and delivers the highest memory bandwidth at the lowest power.

“High-performance applications are driving industry demand for HBM2 DRAM technology. At 256GB/s bandwidth and 66% lower energy per bit, HBM2 opens up new application domains which were previously unimaginable,” said Kevin Widmer, Vice President, Technical Marketing, SK Hynix America. “Combining high-performance FPGAs and HBM2 into a single SiP represents a significant milestone in offering energy-efficient, high-bandwidth compute capabilities.”

Customers can get started on their Stratix 10 designs today using the Fast Forward Compile performance evaluation tools. Altera will start shipping Stratix 10 FPGAs and SoCs in 2016 and Stratix 10 DRAM SiP products will start shipping in 2017.

Comments are closed, but trackbacks and pingbacks are open.